标签:架构 简介 cache ARM Cortex L1 Arm architecture

ARM架构简介

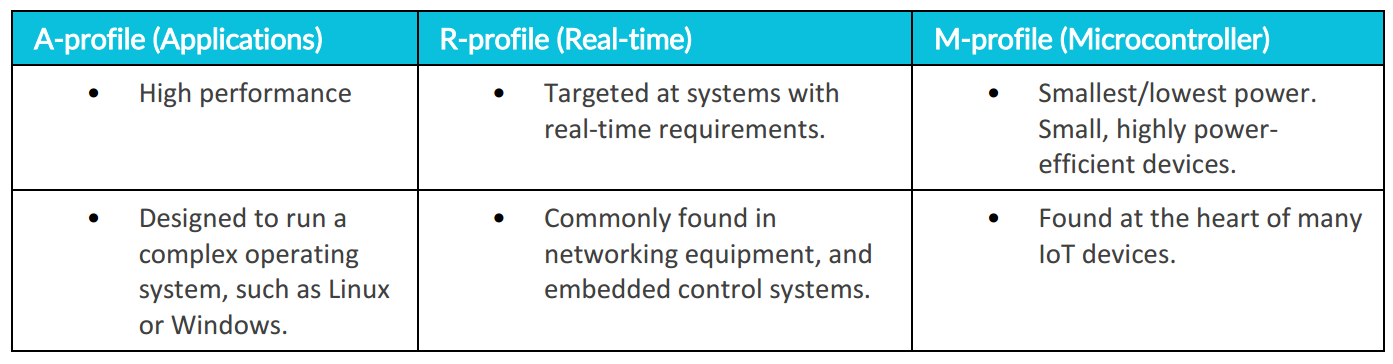

Arm architesture分为三种系类(profiles):

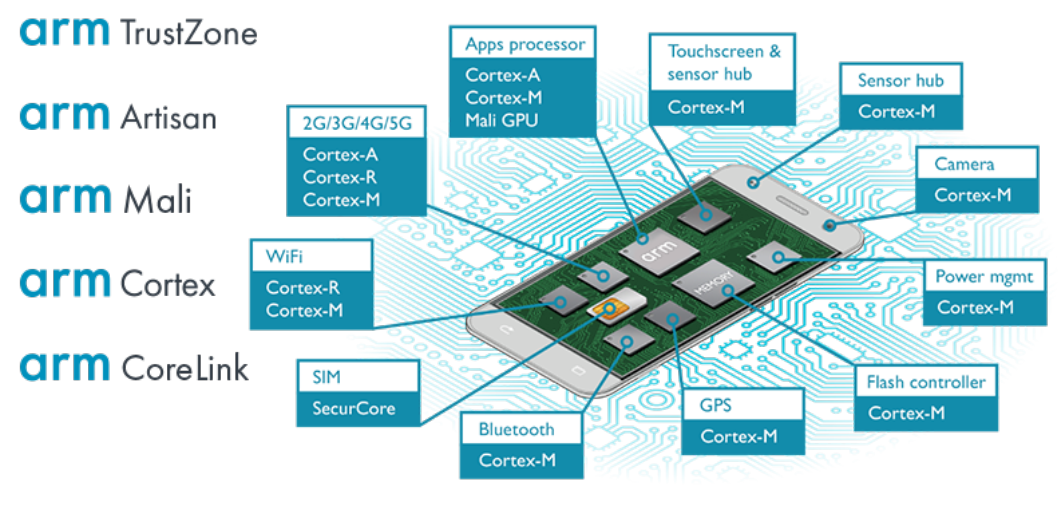

不同系类的应用情况:

Arm Cortex是Arm architecture对应处理器产品的商标名,就和奔腾,酷睿一样

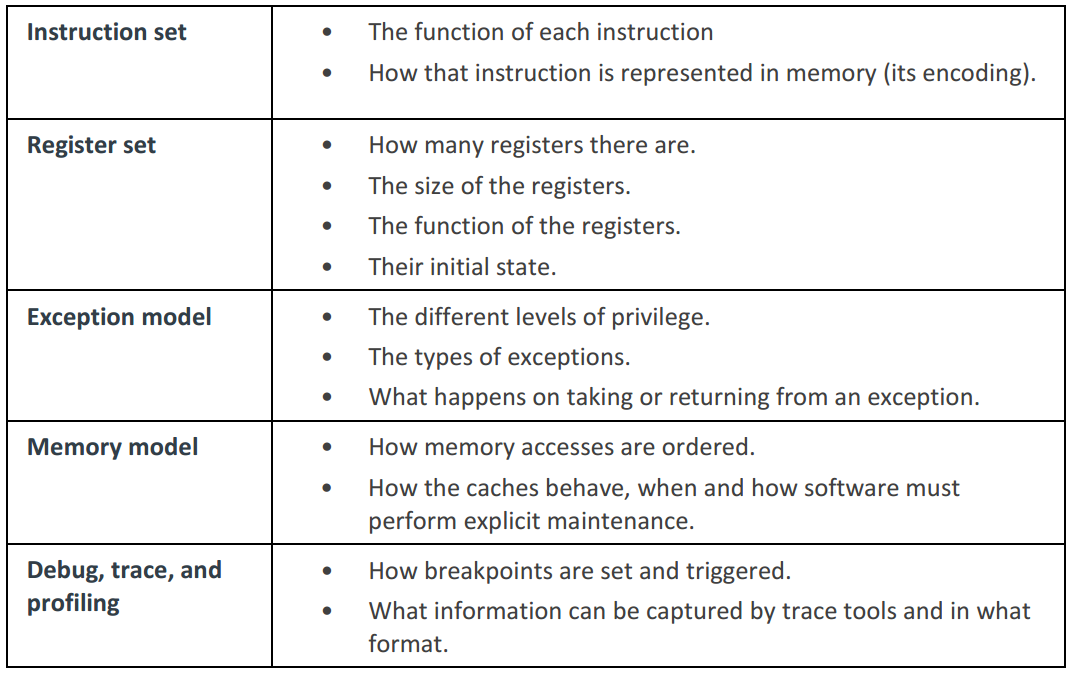

架构是对一个处理器的功能性规范,functional specification,定义how a processor will behave。也可以把它理解为软件和硬件之间的一个桥梁,规范硬件提供一些什么样的功能来供软件所调用。

架构规范如下东西:

除此之外,还有一些特性是可选的,这部分由微架构micro-architecture 所决定,微架构包括但不限于如下:

- Pipeline length and layout.

- Number and sizes of caches.

- Cycle counts for individual instructions.

- Which optional features are implemented.

比如Cortex-A53和Cortex-A72都属于Armv8-A架构architecture,但是他们属于不同的微架构micro-architectures

| Cortex-A53 | Cortex-A72 | |

|---|---|---|

| Target | Optimized for power efficiency | Optimized for performance |

| Pipeline | 8 stages In-order |

15+ stages Out-of-order |

| Caches | L1 I cache: 8KB - 64KB L1 D cache: 8KB - 64KB L2 cache: optional, up to 2MB |

L1 I cache: 48KB fixed L1 D cache: 48KB fixed L2 cache: mandatory, up to 2MB |

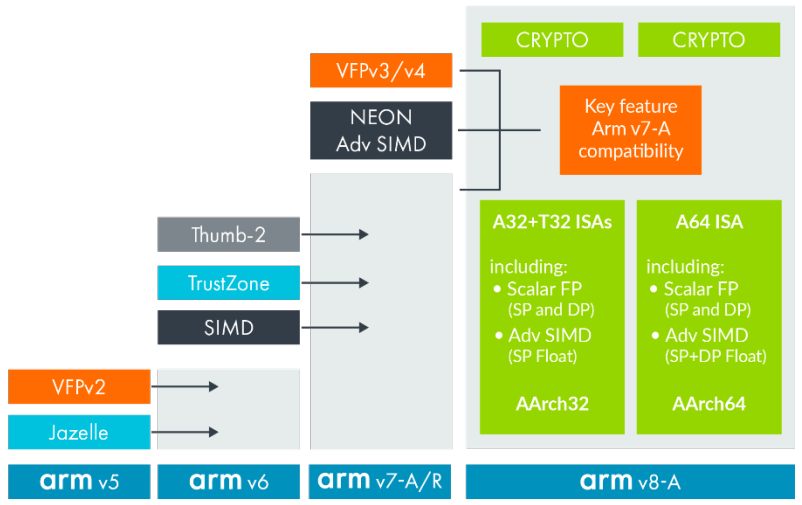

Arm架构发展

标签:架构,简介,cache,ARM,Cortex,L1,Arm,architecture 来源: https://www.cnblogs.com/willhua/p/13458455.html

本站声明: 1. iCode9 技术分享网(下文简称本站)提供的所有内容,仅供技术学习、探讨和分享; 2. 关于本站的所有留言、评论、转载及引用,纯属内容发起人的个人观点,与本站观点和立场无关; 3. 关于本站的所有言论和文字,纯属内容发起人的个人观点,与本站观点和立场无关; 4. 本站文章均是网友提供,不完全保证技术分享内容的完整性、准确性、时效性、风险性和版权归属;如您发现该文章侵犯了您的权益,可联系我们第一时间进行删除; 5. 本站为非盈利性的个人网站,所有内容不会用来进行牟利,也不会利用任何形式的广告来间接获益,纯粹是为了广大技术爱好者提供技术内容和技术思想的分享性交流网站。