标签:LEDR MUXDFF HDLbits SW module q4b Exams KEY input

Description:

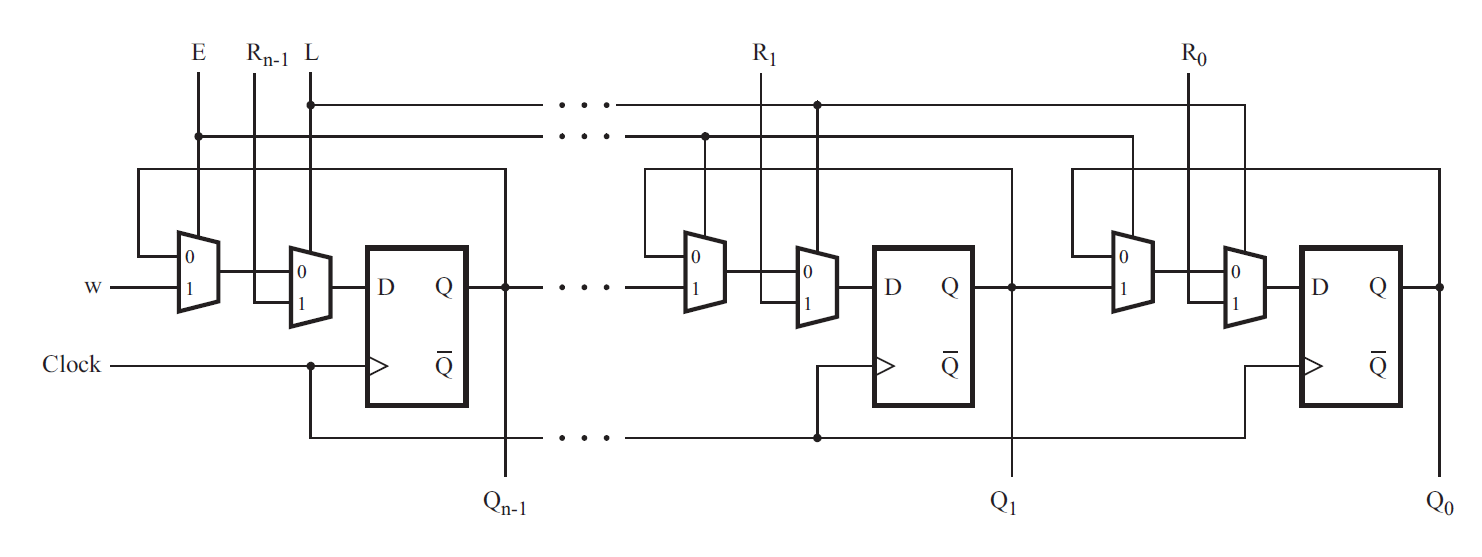

Consider the n-bit shift register circuit shown below:

Write a top-level Verilog module (named top_module) for the shift register, assuming that n = 4. Instantiate four copies of your MUXDFF subcircuit in your top-level module. Assume that you are going to implement the circuit on the DE2 board.

- Connect the R inputs to the SW switches,

- clk to KEY[0],

- E to KEY[1],

- L to KEY[2], and

- w to KEY[3].

- Connect the outputs to the red lights LEDR[3:0].

(Reuse your MUXDFF from exams/2014_q4a.)

module top_module (

input [3:0] SW,

input [3:0] KEY,

output [3:0] LEDR

); //

MUXDFF s1(KEY[3],KEY[1],SW[3],KEY[2],KEY[0],LEDR[3]);

MUXDFF s2(LEDR[3],KEY[1],SW[2],KEY[2],KEY[0],LEDR[2]);

MUXDFF s3(LEDR[2],KEY[1],SW[1],KEY[2],KEY[0],LEDR[1]);

MUXDFF s4(LEDR[1],KEY[1],SW[0],KEY[2],KEY[0],LEDR[0]);

endmodule

module MUXDFF (

input w,

input e,

input r,

input l,

input clk,

output q);

always@(posedge clk)begin

case({e,l})

2'b00:q<=q;

2'b01:q<=r;

2'b10:q<=w;

2'b11:q<=r;

endcase

end

endmodule

标签:LEDR,MUXDFF,HDLbits,SW,module,q4b,Exams,KEY,input 来源: https://www.cnblogs.com/tao1997/p/15520342.html

本站声明: 1. iCode9 技术分享网(下文简称本站)提供的所有内容,仅供技术学习、探讨和分享; 2. 关于本站的所有留言、评论、转载及引用,纯属内容发起人的个人观点,与本站观点和立场无关; 3. 关于本站的所有言论和文字,纯属内容发起人的个人观点,与本站观点和立场无关; 4. 本站文章均是网友提供,不完全保证技术分享内容的完整性、准确性、时效性、风险性和版权归属;如您发现该文章侵犯了您的权益,可联系我们第一时间进行删除; 5. 本站为非盈利性的个人网站,所有内容不会用来进行牟利,也不会利用任何形式的广告来间接获益,纯粹是为了广大技术爱好者提供技术内容和技术思想的分享性交流网站。